Power Management in Chiplet Chip Design: The Complex Trade-offs of Heterogeneous Integration

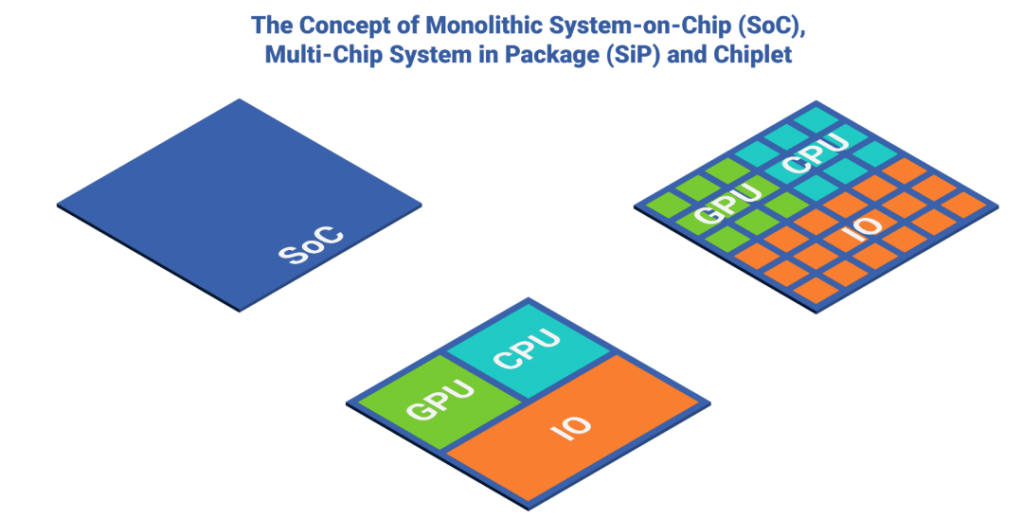

As chip design moves toward heterogeneous assembly and 3D-IC technology, providing and managing power has become a core challenge in chip manufacturing, significantly increasing design complexity and forcing manufacturers to make difficult trade-offs between performance, reliability, and cost.

With the rapid expansion of AI applications and the continuous increase in transistor density, chip power consumption issues have expanded from traditional single-chip SoCs to multi-chip systems, introducing new challenges such as voltage drops, thermal management, and power integrity.

We delve into the power challenges in heterogeneous chip design from two dimensions: the evolution of power management complexity and the strategies and technological innovations to address it, exploring their profound implications for the future development of the semiconductor industry.

The Evolution of Power Management Complexity

With the surge in AI and complex computational demands, chip design is shifting from planar SoCs to heterogeneous chip assembly. This transition significantly enhances performance potential but also makes power management more complex than ever.

In traditional monolithic SoCs, power consumption issues primarily stem from thermal effects caused by transistor density and node scaling. In heterogeneous systems, however, the increased number of chips, thinner materials, and high-density stacking exacerbate the concentration of power demands.

For example, the power consumption of a single SoC has reached hundreds of watts, and the dense integration of multi-chip systems pushes this figure to even higher levels, while requiring stable operation at lower voltages—a challenge that imposes stricter demands on power network design.

High-speed interfaces and interposer layers between chips in heterogeneous systems increase the number of packaging layers, further reducing voltage regulation efficiency and causing capacitance distribution and current transmission to become bottlenecks.

Compared to traditional designs, this architecture not only amplifies the impact of voltage drops and thermal effects but also introduces new issues such as low-frequency power noise, making local optimization of a single chip insufficient to meet overall requirements.

● Power integrity (PI) challenges are particularly prominent in this context.

Since multiple chips share the power grid, voltage drops are no longer isolated phenomena but involve a complex network of hundreds or even thousands of connection points across the entire system.

Thermal gradients, parasitic effects, and dynamic load changes further exacerbate this issue, especially in 3D-ICs, where high current density and thin substrate designs may lead to uneven power distribution and accelerated device aging.

Meanwhile, the lack of unified power simulation standards makes design verification exceptionally challenging, and traditional partitioned analysis methods are no longer suitable for the global characteristics of multi-chip systems.

This complexity requires designers to perform joint simulation of the entire system at an early stage, but this demands significant computational resources and time investment, potentially increasing development costs.

● Power challenges in heterogeneous chip design are also reflected in the diversity of manufacturing and processes.

Different chips may come from different foundries, and process differences and manufacturing variability (such as bump height and bonding quality) can lead to asymmetric power distribution.

The demand for high-speed data transmission between chips has driven the intensive use of microbumps and through-silicon vias (TSVs), but the number and layout of these connection points directly impact power consumption and thermal management capabilities, further complicating design trade-offs.

In this context, power management is no longer a single technical issue but a comprehensive challenge involving architecture, packaging, and system-level coordination.

Strategies and technological innovations

In response to power challenges in heterogeneous chip designs, the industry is exploring various innovative methods to balance performance and energy efficiency, with early planning and co-simulation emerging as key strategies.

In traditional SoC designs, power network modeling is relatively straightforward, typically optimized based on known packaging parameters. However, multi-chip systems require consideration of the interactions between interposers, packaging substrates, and other chips from the outset of design.

Through hypothesis analysis and rapid simulation tools, designers can assess the impact of different packaging styles (such as 2.5D or 3D-IC) on power integrity and optimize the number of microbumps and decoupling capacitor distribution. While this approach increases upfront effort, it significantly reduces the risk of redesign later in the process.

Additionally, hierarchical modeling techniques have been introduced to address the surge in simulation scale, such as simulating chips, interposers, and packaging separately using chip power models (CPM), followed by system-level joint analysis to balance accuracy and efficiency.

● Technological innovations are also driving advancements in power management.

Technologies such as backside power delivery (BPSD) and interposer-integrated capacitors are considered effective means to mitigate voltage drop and thermal issues.

◎ BPSD improves current transmission efficiency by relocating the power network to the chip’s backside, reducing front-side routing congestion;

◎ Interposer capacitors shorten the distance between decoupling capacitors and active circuits, enhancing high-frequency noise suppression capabilities.

◎ Meanwhile, Adaptive Voltage Scaling (AVS) and Dynamic Voltage and Frequency Scaling (DVFS) are widely applied in dynamic load management, enabling chips to adjust power consumption in real-time based on workload.

◎ Additionally, thermal-aware design is increasingly becoming an industry consensus, mitigating the impact of local hotspots on power integrity through optimized chip layout and collaborative thermal-electrical simulation.

While the application of these technologies increases packaging complexity, they open up new possibilities for performance enhancement and energy efficiency optimization.

Early planning requires support from more advanced EDA tools, but current toolchains still lack sufficient capabilities in multi-chip co-simulation and low-frequency noise analysis.

Manufacturing variability and process mismatch increase design uncertainty, forcing designers to collaborate more closely with foundries and packaging vendors to obtain accurate interconnect models and thermal characteristic data.

AI and machine learning are seen as potential aids for design optimization, capable of accelerating trade-off analysis through historical data, but their large-scale application in power management still requires time to validate. Power management for heterogeneous chips is driving the industry toward a system-level mindset, requiring designers to shift from a single-chip perspective to global optimization.

Summary

The advent of heterogeneous chip design has pushed power management to the forefront of challenges in the semiconductor industry. The evolution from single-chip SoCs to multi-chip systems has not only amplified issues such as voltage drops, thermal effects, and power integrity but also reshaped design logic through high-density integration and complex computational demands.

The combination of early planning, co-simulation, and innovative technologies (such as back-side powering and dynamic regulation) provides a feasible path to address these challenges, but also exposes shortcomings in toolchains, standardization, and manufacturing collaboration.

Breakthroughs in power management will become a key variable in semiconductor performance improvements over the next few years, directly impacting the implementation of applications in fields such as AI, automotive, and edge computing.

Leave a comment